##

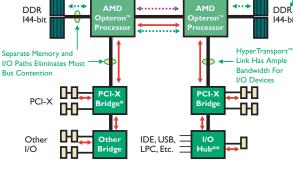

## AMD Opteron<sup>™</sup> Processor-based Server HyperTransport<sup>™</sup> HyperTransport<sup>™</sup> Technology Buses **Technology Buses Enable** for Direct Connection of CPUs Direct Connection of CPUs Memory Capacity for up to 8 Sockets Scales w/ Number of Processors AMD DDR DDR l44-bit l44-bit \$ \$1 \$ \$1 DDR **....** 4----DDR l44-bit l44-bit Optero

Fewer Chips Needed for a 4-Socket Server (Reduces Cost)

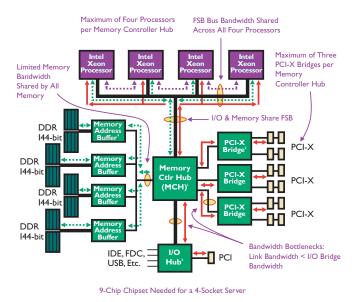

## Intel Xeon MP Processor-based Server

|                                | AMD Opteron Processor-based Server                                                                                                                                                                                                                                                                                              | Intel Xeon MP Processor-based Server                                                                                                                                                                                                                     |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture                   | <ul> <li>AMD64 with Direct Connect Architecture</li> <li>Direct connection of CPUs for up to 8 sockets</li> <li>Provides simultaneous high-performance 32- and 64-bit computing</li> <li>Increases memory performance, provides more balanced I/O throughput, and allows for more linear symmetrical multiprocessing</li> </ul> | <ul> <li>IA32 Architecture</li> <li>High-performance 32-bit computing only</li> <li>Businesses needing 64-bit benefits must switch to a new architecture</li> </ul>                                                                                      |

| Memory<br>Access<br>Technology | <ul> <li>Integrated Memory Controller</li> <li>Memory is directly connected to the CPU providing optimized memory performance</li> <li>Provides low-latency memory access and bandwidth that scales as processors are added</li> </ul>                                                                                          | <ul> <li><b>"Northbridge"-style Memory Controller via Front Side Bus</b></li> <li>Passage through memory controller hub delays memory reads</li> <li>Processors compete for FSB bandwidth</li> <li>8-socket solutions require even more chips</li> </ul> |

| Primary Bus<br>Technology      | <ul> <li>HyperTransport<sup>™</sup> Technology</li> <li>At up to 6.4GB/s bandwidth per link, designed to provide a high-speed connection between processors and core logic with sufficient bandwidth for supporting new and existing interconnects</li> </ul>                                                                   | <ul> <li>Proprietary Hub I/O Buses</li> <li>Bridge and hub devices can be overwhelmed by the I/O demands of attached peripherals</li> </ul>                                                                                                              |

|                                | * AMD 0121™ I LaTura-a™ DCL V Tura-I                                                                                                                                                                                                                                                                                            | Seman Menter CMIC LIE Managerie Canada II. (MCLI)                                                                                                                                                                                                        |

Key

Memory Traffic

I/O Traffic IPC Traffic ·----

4....

\* AMD-8131<sup>™</sup> HyperTransport<sup>™</sup> PCI-X Tunnel \*\* AMD-8111<sup>™</sup> HyperTransport I/O Hub <sup>1</sup>ServerWorks CMIC HE Memory Controller Hub (MCH) <sup>2</sup>ServerWorks CIOB-X 64-bit PCI/PCI-X Controller Hub <sup>3</sup>ServerWorks CSB5 I/O Controller Hub <sup>4</sup>ServerWorks REMC Memory Address Buffer